來源——AMP實驗室

不知內存爲何物了

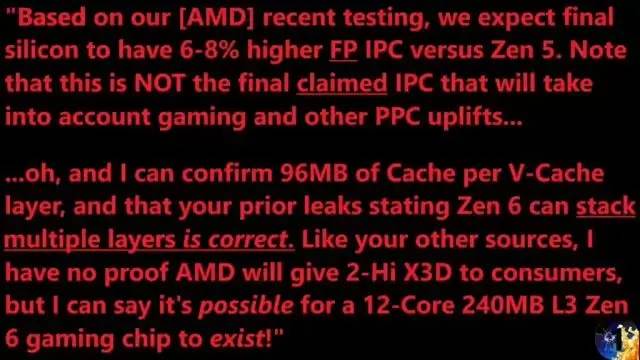

造謠領域大神yt@Moore's Law Is Dead(MLID)在最新一期視頻中,曝料稱 AMD 將變革 Zen 6 架構,通過多層 3D 堆疊緩存,相比較 Zen 5 架構,FP IPC (浮點運算每時鐘指令數) 增幅可達到 6~8%。

在 Zen 5 架構上,每個 3D V-Cache 層最高可以緩存 64MB,而在 Zen 6 架構上,增加到 96MB。

此外 AMD 還計劃重新設計芯粒(chiplets),每個核心複合芯片(CCD)可以容納 12 核,意味着消費級桌面和筆記本電腦最多能擁有 24 個核心。

在單 CCD Ryzen 處理器上,由於 CCD 包含 48MB(每個核心 4MB)和一層 3D V-Cache(96MB)計算,其 L3 緩存可以達到 144MB(48+96)。

如果按照堆疊雙 3D V-Cache 計算,那麼 L3 緩存最高可以達到 240MB(96 + 96 + 48)。此外,Zen 6 架構還預計將帶來更高的核心頻率和更多的核心數量,結合先進的臺積電製程工藝,這將使其在性能上更具競爭力。

更多遊戲資訊請關註:電玩幫遊戲資訊專區

電玩幫圖文攻略 www.vgover.com