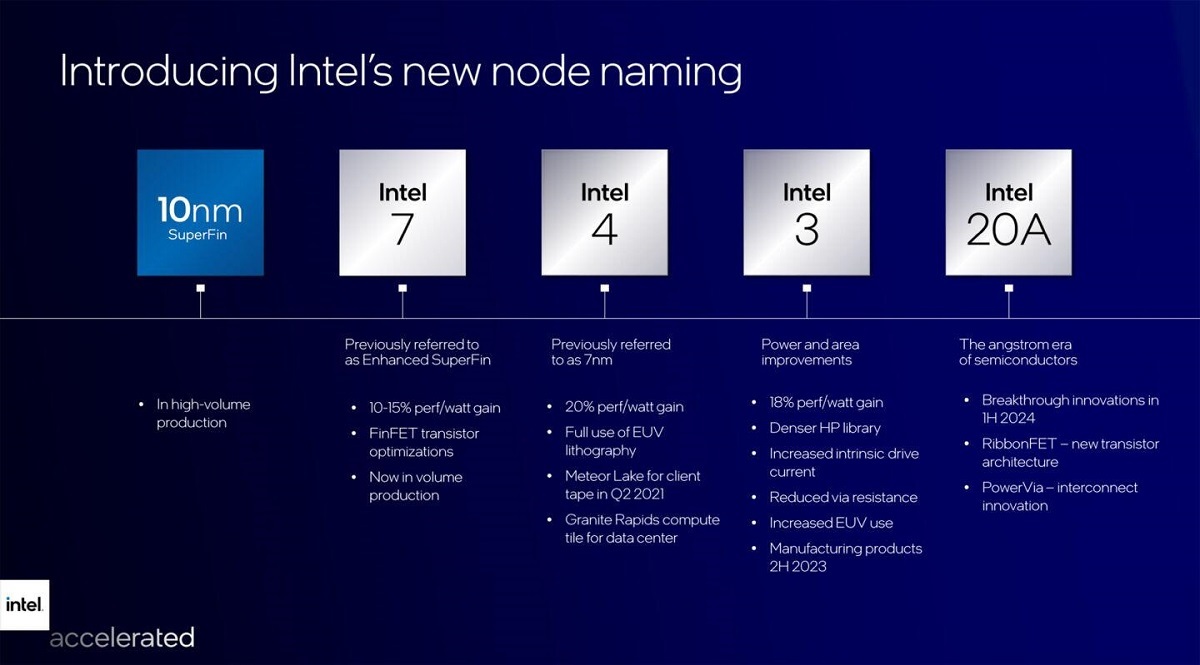

在两年前的“英特尔加速创新:制程工艺和封装技术线上发布会”上,英特尔CEO帕特-基尔辛格(Pat Gelsinger)雄心勃勃地公布了最新工艺路线图,力求在四年里迈过5个制程节点,分别是Intel 7、Intel 4、Intel 3、Intel 20A和Intel 18A,目标半导体制造工艺可以在2025年赶上台积电(TSMC),同时围绕“IDM 2.0”战略打造世界一流的英特尔代工服务(IFS)。

英特尔在过去两年里,多次表示先进工艺开发方面进展顺利。今年3月,英特尔高级副总裁兼中国区董事长王锐在接受媒体采访时表示,Intel 20A和Intel 18A工艺制程已测试流片,并坚信到2025年能够重新回领先地位。不过近日有分析师透露,高通可能已停止设计基于Intel 20A工艺的芯片,意味着Intel 18A工艺的研发和量产将面临更高的不确定性和风险。

如果消息属实,相信对于雄心勃勃的英特尔来说是一个严重的打击。今年3月,英特尔才和Arm达成了协议,让芯片设计者能够基于Intel 18A工艺打造低功耗的SoC,首先聚焦的便是移动设备,而高通恰恰是该领域的龙头企业。

按照英特尔的计划,将在Intel 20A制程节点首次引入RibbonFET和PowerVia两大突破性技术,从而开启埃米时代。其中RibbonFET是对全环绕栅极晶体管(Gate All Around)的实现,将成为英特尔自2011年推出FinFET以来的首个全新晶体管架构。该技术加快了晶体管开关速度,同时实现与多鳍结构相同的驱动电流,但占用的空间更小。PowerVia是英特尔独有的、业界首个背面电能传输网络,通过消除晶圆正面供电布线需求来优化信号传输。

数天前,英特尔还发文专门介绍了PowerVia技术。英特尔表示,应用新技术后,芯片制造更像三明治,首先还是制造晶体管,然后添加互连层,接着翻转晶圆并进行打磨,在晶体管底层接上电源线。背面供电一方面让晶体管供电的路径变得非常直接,可以减少信号串扰,降低功耗,将平台电压降低优化30%。另一方面,解决了晶体管尺寸不断缩小带来的互连瓶颈,实现了6%的频率增益和超过90%的标准单元利用率。此外,英特尔还开发了全新的散热技术,并在基于Intel 4的、经过充分验证的测试芯片上进行了反复调试,测试芯片展示了良好的散热特性,PowerVia能达到了相当高的良率和可靠性指标。

更多游戏资讯请关注:电玩帮游戏资讯专区

电玩帮图文攻略 www.vgover.com