2026年1月16日,據科技媒體NeoWin援引美國商標和專利局(USPTO)公示信息報道,AMD近日獲得一項名爲《均衡延遲堆疊緩存》(Balanced Latency Stacked Cache)的專利授權。該專利標誌着AMD計劃將成熟的3D堆疊技術從現有L3緩存場景,進一步拓展至L2緩存領域,有望爲處理器性能與能效帶來雙重提升。

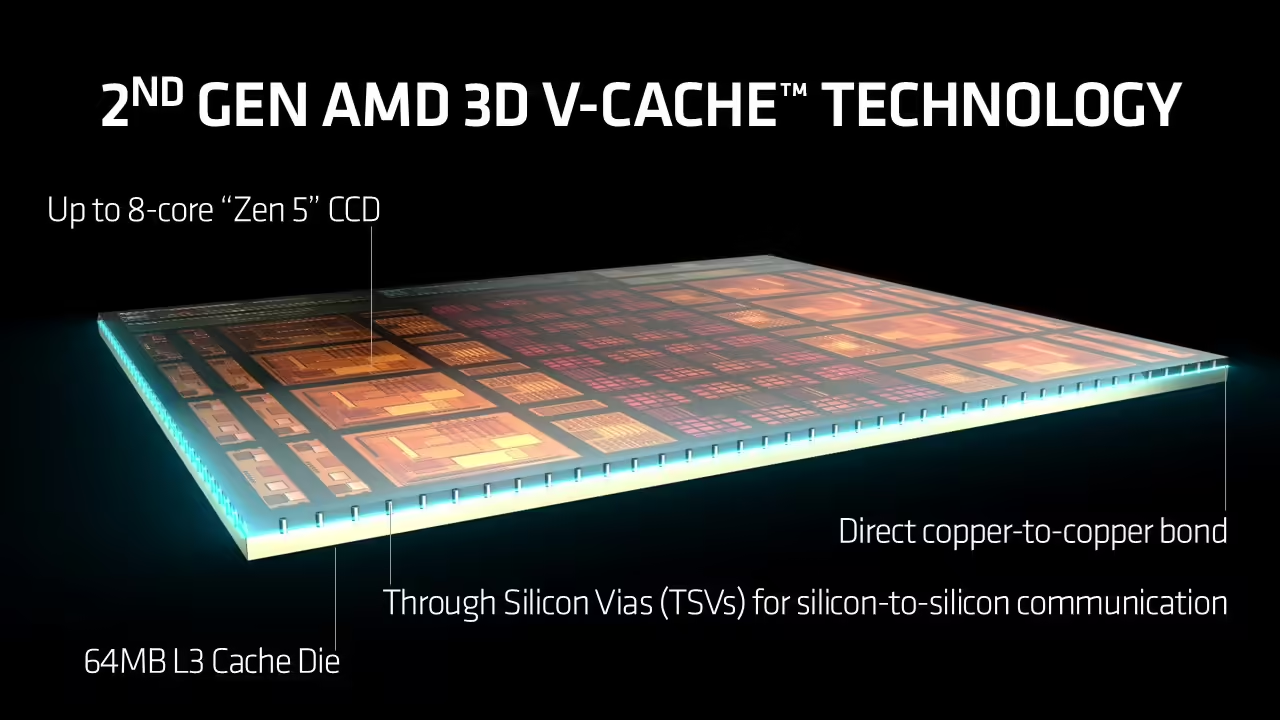

作爲CPU內部關鍵的數據緩衝部件,L2緩存常被比作核心運算單元的“近距中轉站”,其速度介於L1緩存與內存之間,是保障處理器數據吞吐效率的重要防線。相較於內存,L2緩存擁有更快的響應速度,而其容量與訪問延遲直接決定了CPU核心獲取數據的效率,對整體運算性能影響深遠。此前,AMD的3D堆疊技術僅應用於Ryzen X3D系列處理器的L3緩存(LLC),通過3D V-Cache技術顯著提升了遊戲及專業應用的運行表現。

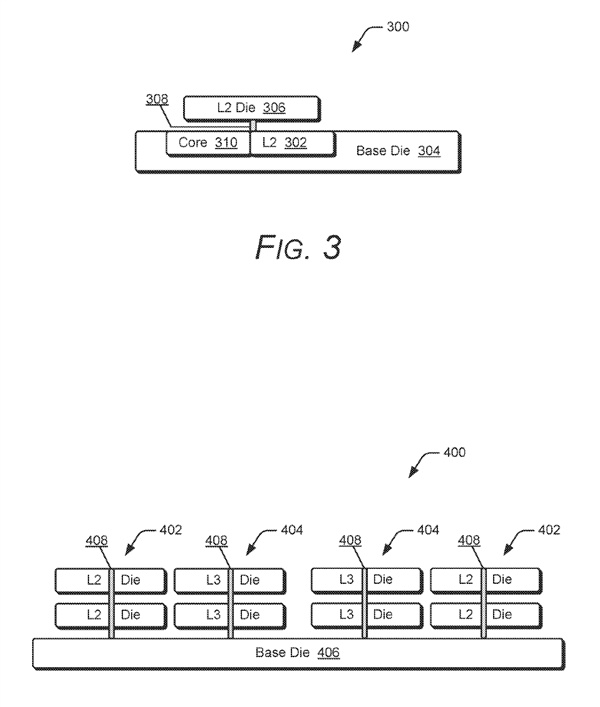

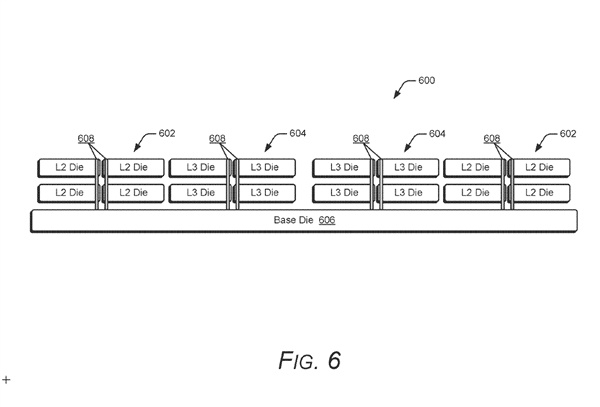

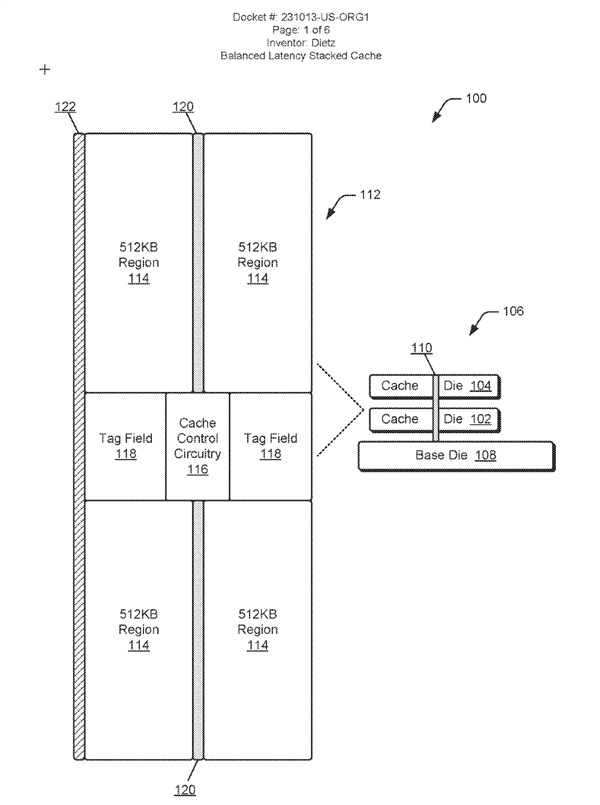

此次曝光的新專利,展現了AMD在緩存技術上的進一步探索。與現有方案不同,該技術通過垂直堆疊L2緩存芯片的方式,針對性降低數據訪問延遲並優化能效表現。專利文件顯示,AMD工程師計劃採用硅通孔(TSV)或鍵合焊盤過孔(BPV)等先進互聯技術,在堆疊芯片間構建高效垂直通信通道,這一技術路徑也與行業內三維集成封裝的發展趨勢相契合。

AMD在該設計中採用了創新性的結構佈局,將互聯過孔佈置於堆疊芯片的幾何中心。這種對稱均衡的設計思路,不僅能夠縮短電路佈線長度與信號傳輸層級,更能確保各層緩存間的數據訪問時間保持一致,從而最大限度降低信號損耗與延遲波動,爲性能穩定性提供保障。

以1MB規格的L2緩存爲測試對象,採用3D堆疊設計後,數據訪問時鐘週期可從傳統平面緩存的14個縮減至12個。儘管僅減少兩個週期,但在CPU架構設計中,L2緩存訪問週期通常處於10至50個時鐘週期區間,這種幅度的優化已屬於關鍵性突破,有望爲處理器整體運算速度帶來顯著提升,尤其在高負載多線程場景中優勢更爲明顯。

該專利目前編號爲US20260003794A1,仍處於公示階段。雖然理論性能預期樂觀,但從專利落地到量產產品問世,往往需要經歷較長的技術轉化與驗證週期,且實際表現還可能受到芯片製造工藝、散熱設計等多重物理因素影響。

更多遊戲資訊請關註:電玩幫遊戲資訊專區

電玩幫圖文攻略 www.vgover.com