2026年1月16日,据科技媒体NeoWin援引美国商标和专利局(USPTO)公示信息报道,AMD近日获得一项名为《均衡延迟堆叠缓存》(Balanced Latency Stacked Cache)的专利授权。该专利标志着AMD计划将成熟的3D堆叠技术从现有L3缓存场景,进一步拓展至L2缓存领域,有望为处理器性能与能效带来双重提升。

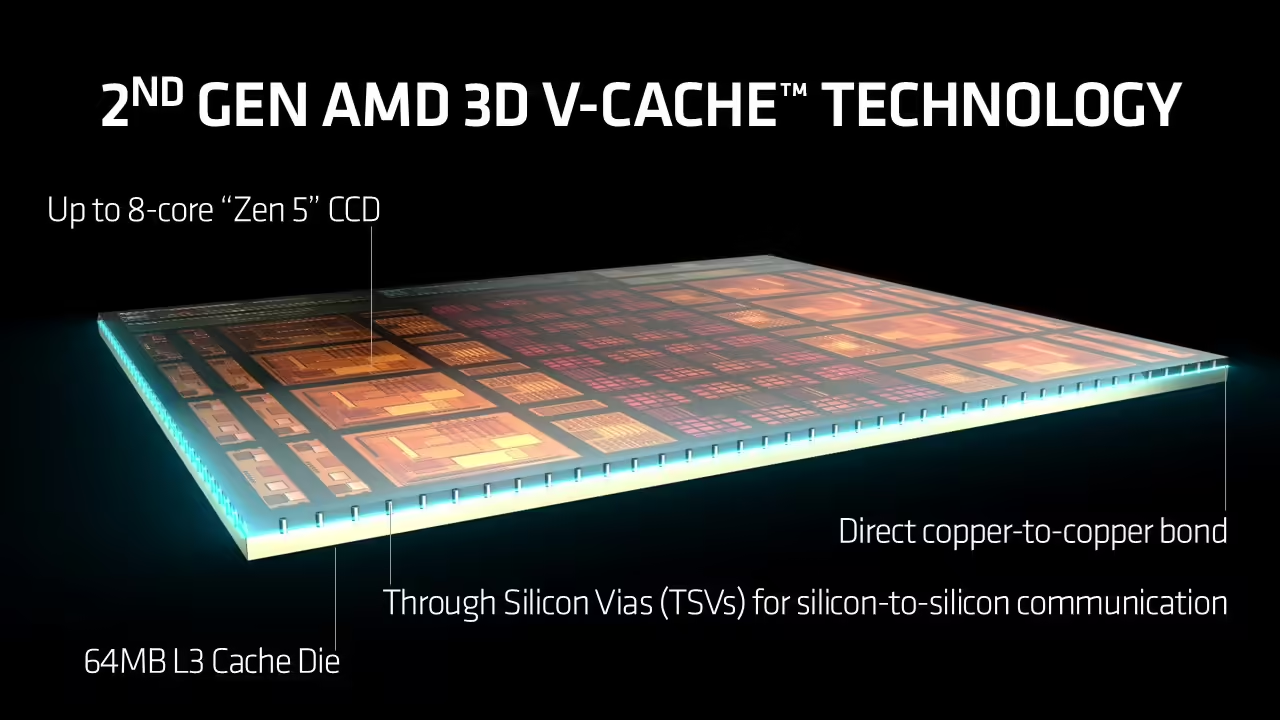

作为CPU内部关键的数据缓冲部件,L2缓存常被比作核心运算单元的“近距中转站”,其速度介于L1缓存与内存之间,是保障处理器数据吞吐效率的重要防线。相较于内存,L2缓存拥有更快的响应速度,而其容量与访问延迟直接决定了CPU核心获取数据的效率,对整体运算性能影响深远。此前,AMD的3D堆叠技术仅应用于Ryzen X3D系列处理器的L3缓存(LLC),通过3D V-Cache技术显著提升了游戏及专业应用的运行表现。

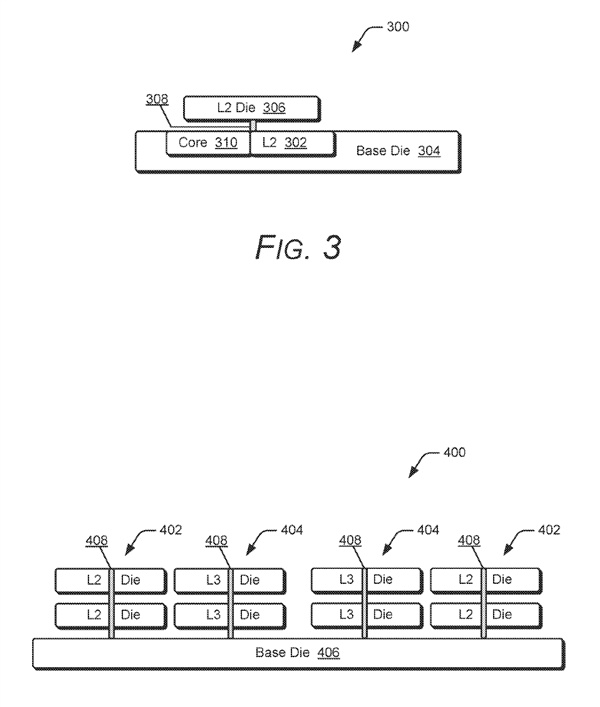

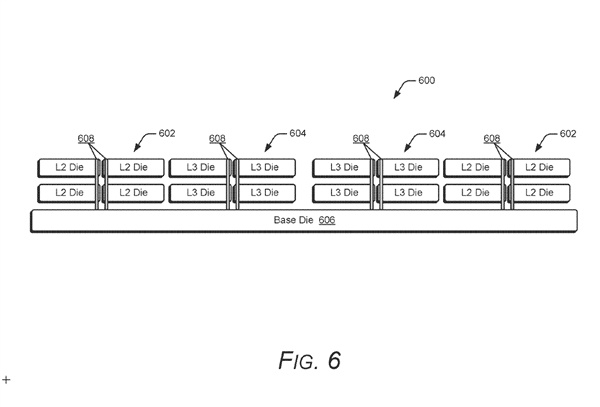

此次曝光的新专利,展现了AMD在缓存技术上的进一步探索。与现有方案不同,该技术通过垂直堆叠L2缓存芯片的方式,针对性降低数据访问延迟并优化能效表现。专利文件显示,AMD工程师计划采用硅通孔(TSV)或键合焊盘过孔(BPV)等先进互联技术,在堆叠芯片间构建高效垂直通信通道,这一技术路径也与行业内三维集成封装的发展趋势相契合。

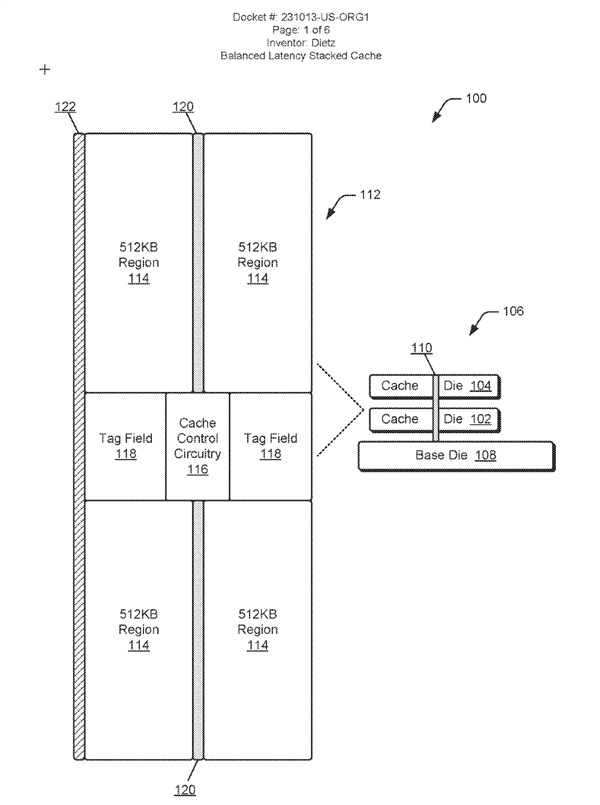

AMD在该设计中采用了创新性的结构布局,将互联过孔布置于堆叠芯片的几何中心。这种对称均衡的设计思路,不仅能够缩短电路布线长度与信号传输层级,更能确保各层缓存间的数据访问时间保持一致,从而最大限度降低信号损耗与延迟波动,为性能稳定性提供保障。

以1MB规格的L2缓存为测试对象,采用3D堆叠设计后,数据访问时钟周期可从传统平面缓存的14个缩减至12个。尽管仅减少两个周期,但在CPU架构设计中,L2缓存访问周期通常处于10至50个时钟周期区间,这种幅度的优化已属于关键性突破,有望为处理器整体运算速度带来显著提升,尤其在高负载多线程场景中优势更为明显。

该专利目前编号为US20260003794A1,仍处于公示阶段。虽然理论性能预期乐观,但从专利落地到量产产品问世,往往需要经历较长的技术转化与验证周期,且实际表现还可能受到芯片制造工艺、散热设计等多重物理因素影响。

更多游戏资讯请关注:电玩帮游戏资讯专区

电玩帮图文攻略 www.vgover.com