來源——AMP實驗室

能不能來個重大利好消息

超大規模集成電路研討會(VLSI Symposium)定於 2025 年 6 月 8 日至 12 日在日本京都舉行,這是半導體領域的頂級國際會議,目前已有44年曆史。在今年4月份,VLSI已發佈了預覽文檔,介紹了一系列將於研討會上公佈的論文,當然也包括了 Intel 18A 工藝技術細節。

英特爾正式在VLSI上詳細介紹了其Intel 18A製造工藝的更多性能數據,該工藝對於公司有極爲重大的意義,並且將於2025年下半年投入量產。不過最近英特爾的新路線表明,公司更大的希望並非是單純18A,而是後續經過優化的18A-P和繼任者14A工藝,18A將僅用於英特爾自家產品。

18A工藝將GAA晶體管和PowerVia背面供電網絡相結合,形成了一種全新的金屬堆疊架構。這樣的設計讓電源佈線至芯片背面,得以讓關鍵層的互連間距縮小,同時放鬆頂層間距,從而提高良率簡化製造流程。

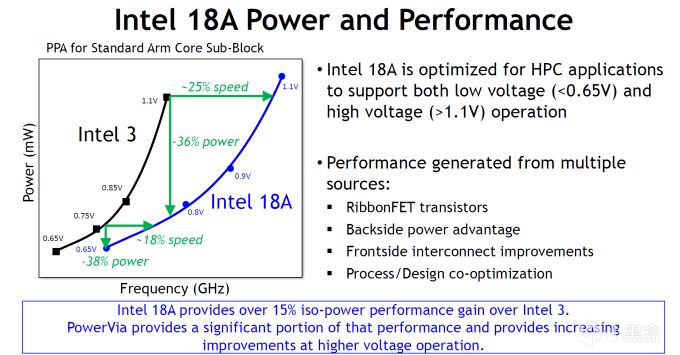

在ARM核心子模塊的標準化功率、性能和麪積測試中,英特爾18A在相同功耗下性能比Intel 3提高了約15%。在1.1V下,其頻率優勢達25%,而在0.75V下,性能優勢來到18%,但其功耗降低了近40%。

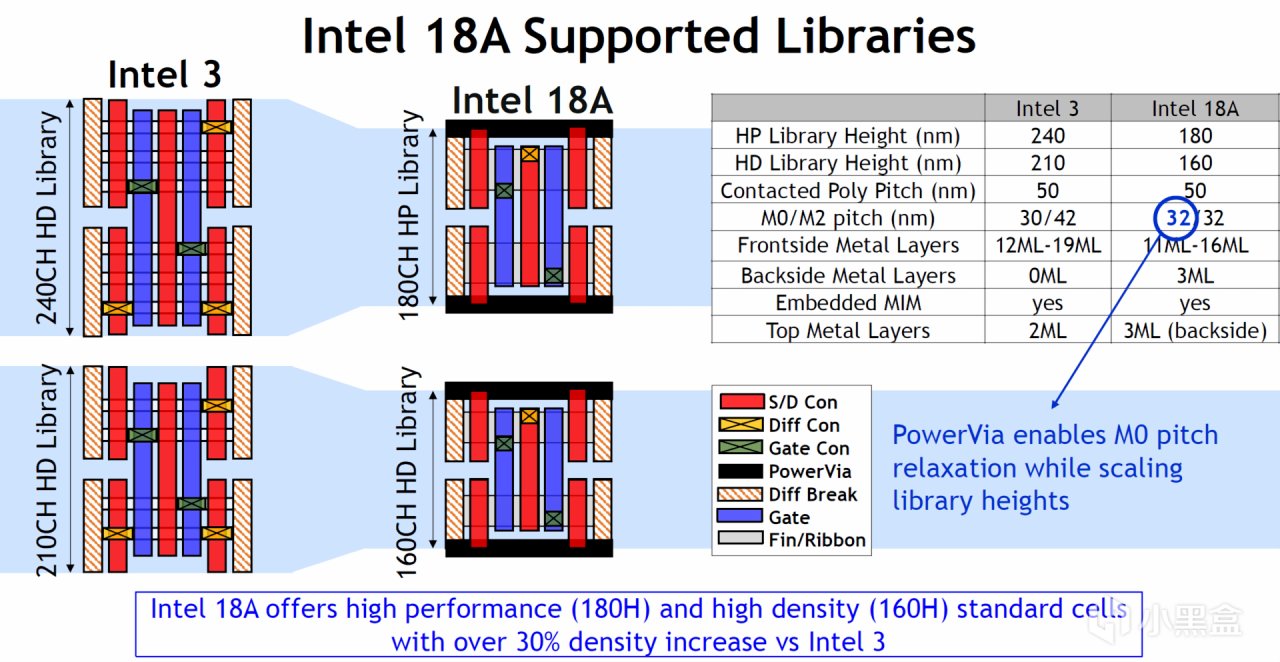

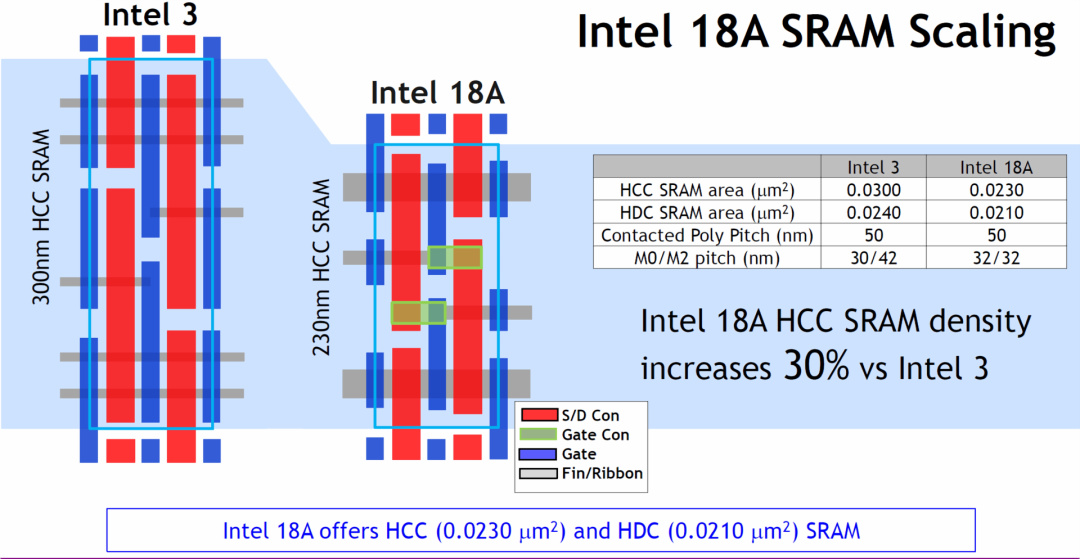

該工藝的底層顯著降低了單元高度:性能調優後的單元高度爲 180 納米,而高密度設計的高度爲 160 納米,兩者均小於前代產品。正面金屬層數從英特爾 3 的 12 至 19 層減少到英特爾 18A 的 11 至 16 層,並增加了三個背面金屬層以支持 PowerVia。

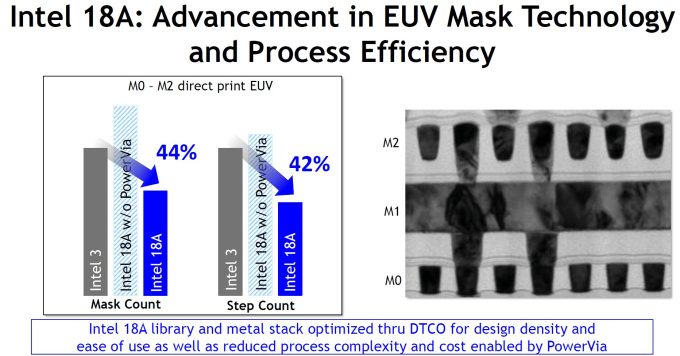

M1 至 M10 層的間距已從 60 納米縮小至 32 納米,之後在上層再次放寬。M0 至 M4 層採用低數值孔徑 EUV 曝光技術,將所需光罩數量減少了 44%,並簡化了製造流程。

英特爾計劃在其今年推出的低功耗“Panther Lake”計算芯片組和僅採用效率核心的 Clearwater Forest Xeon 7 系列中首次推出 18A 工藝。後續被寄予衆望的Nova Lake同樣也基於該工藝。

更多遊戲資訊請關註:電玩幫遊戲資訊專區

電玩幫圖文攻略 www.vgover.com

![任天堂前銷售負責人預判:Switch 2 硬件漲價已成定局[cube_摘墨鏡][cube_摘墨鏡]](https://imgheybox1.max-c.com/bbs/2026/04/05/3b368916849076608f90f840878267fb.jpeg?imageMogr2/auto-orient/ignore-error/1/format/jpg/thumbnail/398x679%3E)