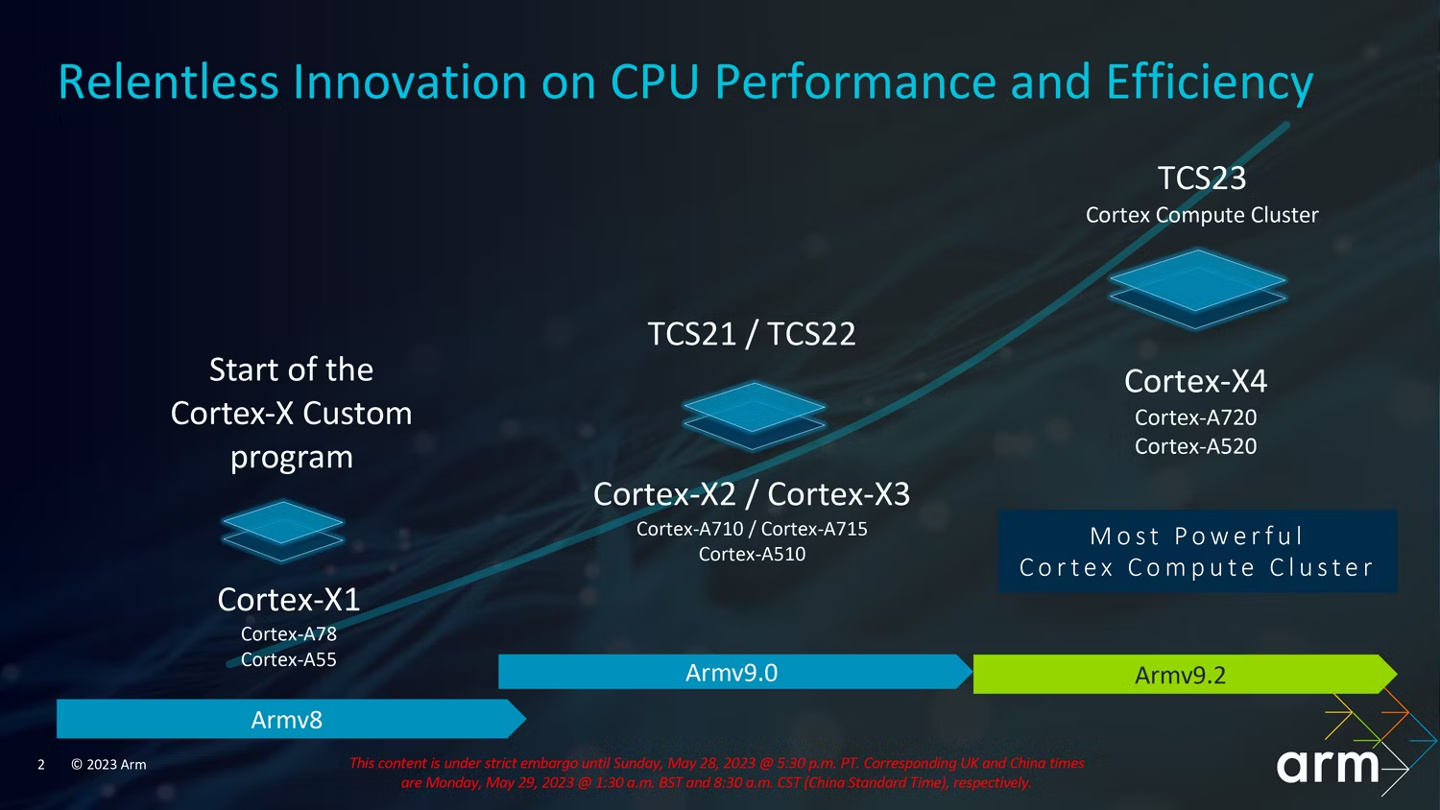

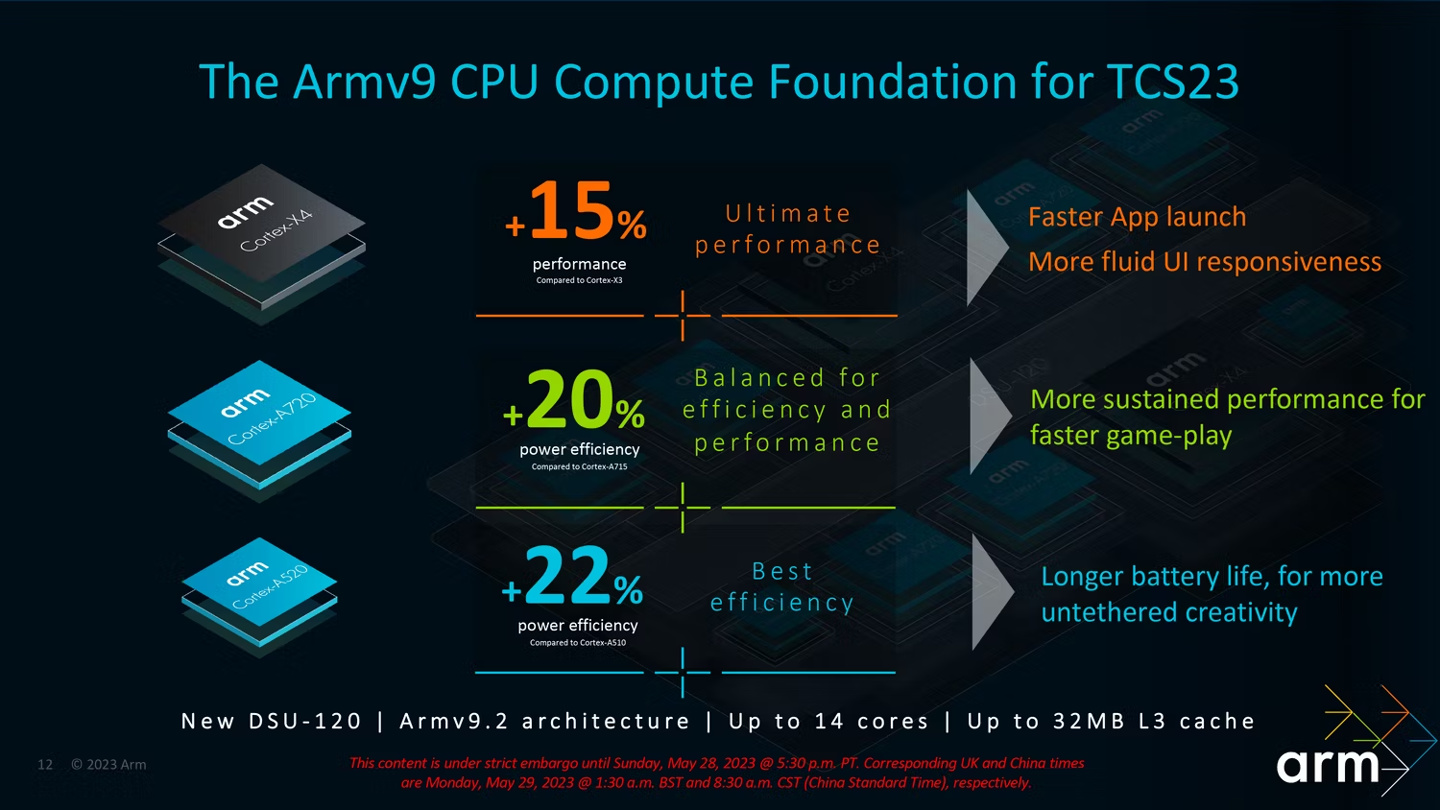

Arm 公司今天發佈了 2023 年的移動處理器核心設計:Cortex-X4、A720 和 A520,這些核心都是基於 Arm v9.2 架構,只支持 64 位指令集,不再兼容 32 位應用。Arm 公司表示,這些核心在性能和效率方面都有顯著的提升,同時也加強了安全性和可擴展性。

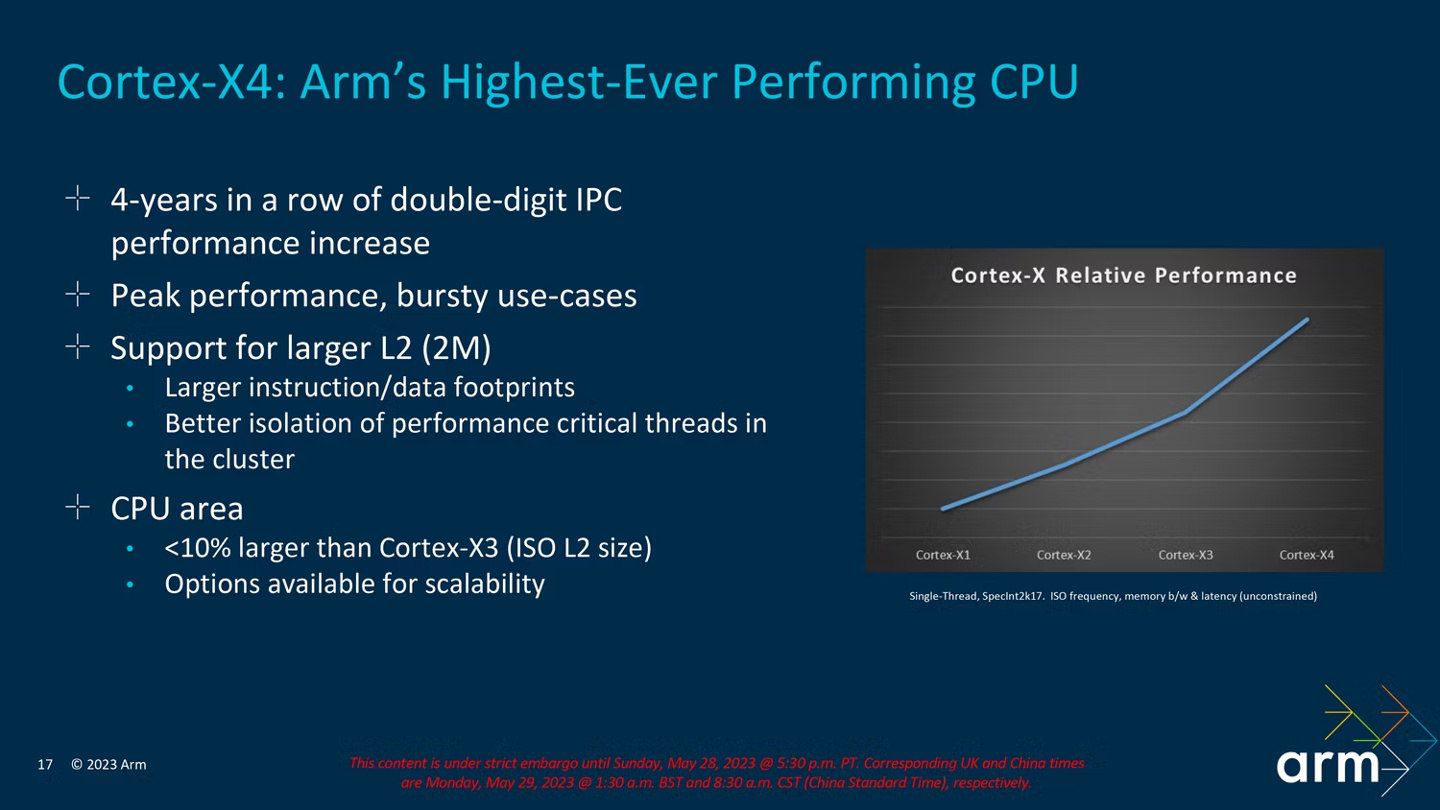

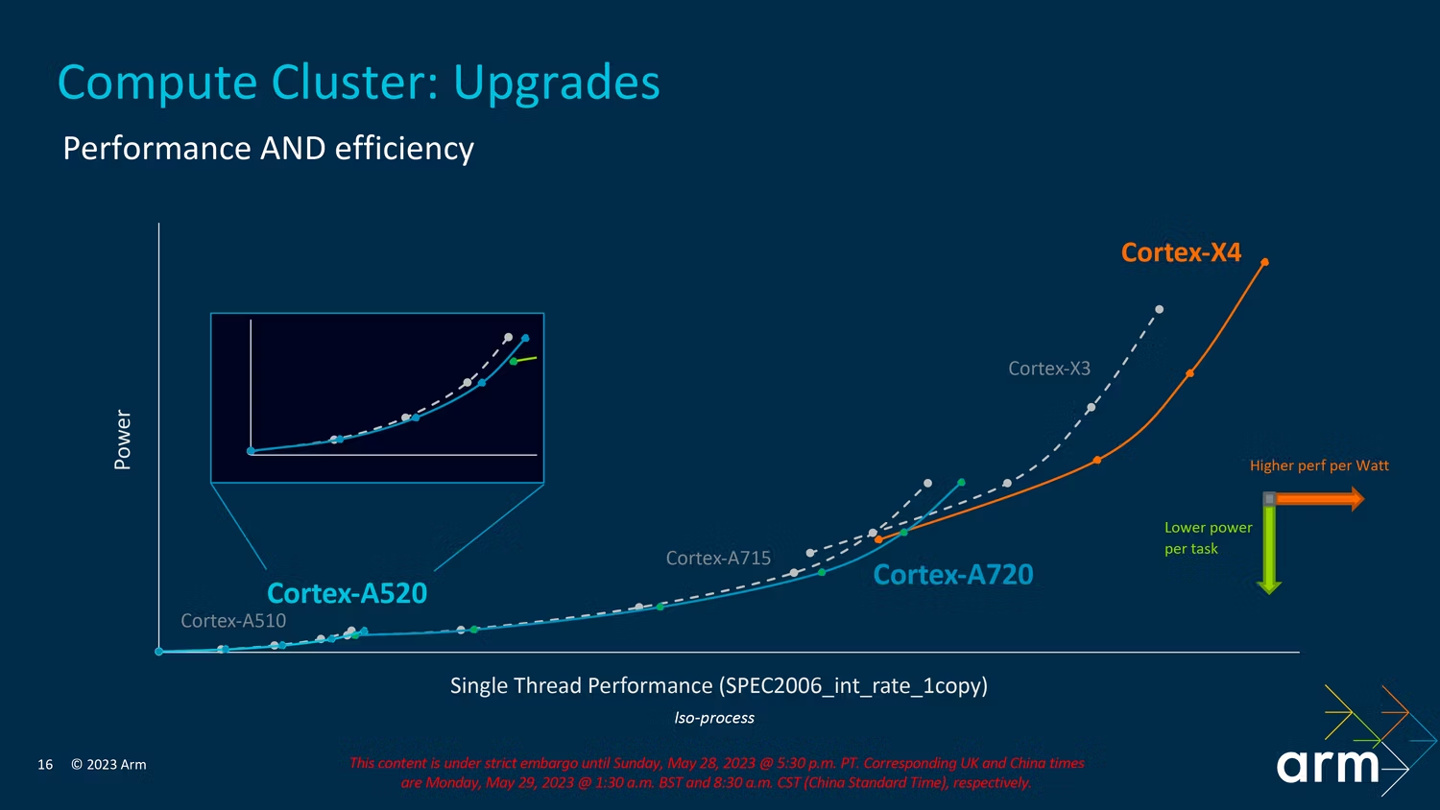

Cortex-X4 是 Arm 公司的旗艦核心,也就是我們常說的超大核心,該核心比去年的 X3 核心性能平均提高了 15%,同時在相同頻率下降低了 40% 的功耗。X4 核心主要針對高性能需求,一般只會有一到兩個這樣的核心用在芯片中。

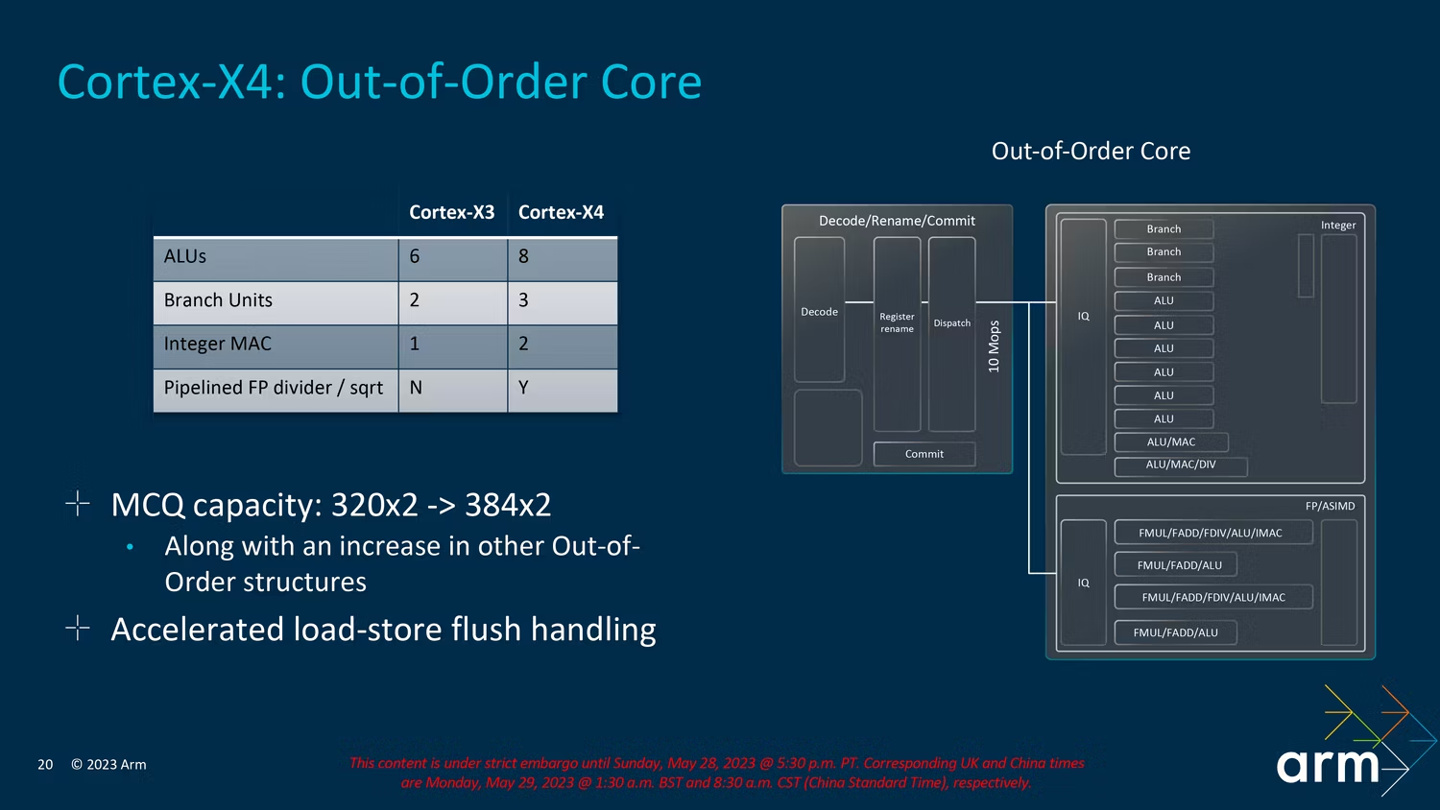

Cortex-X4 的物理尺寸增大了不到 10%,是有史以來最高效的 Cortex-X 內核。2MB 的 L2 緩存大小帶來更高的性能,還將算術邏輯單元 (ALU) 的數量從 6 個增加到 8 個,添加了一個額外的分支單元(總共 3 個),添加了一個額外的乘法累加器單元,以及流水線浮點和平方根運算。

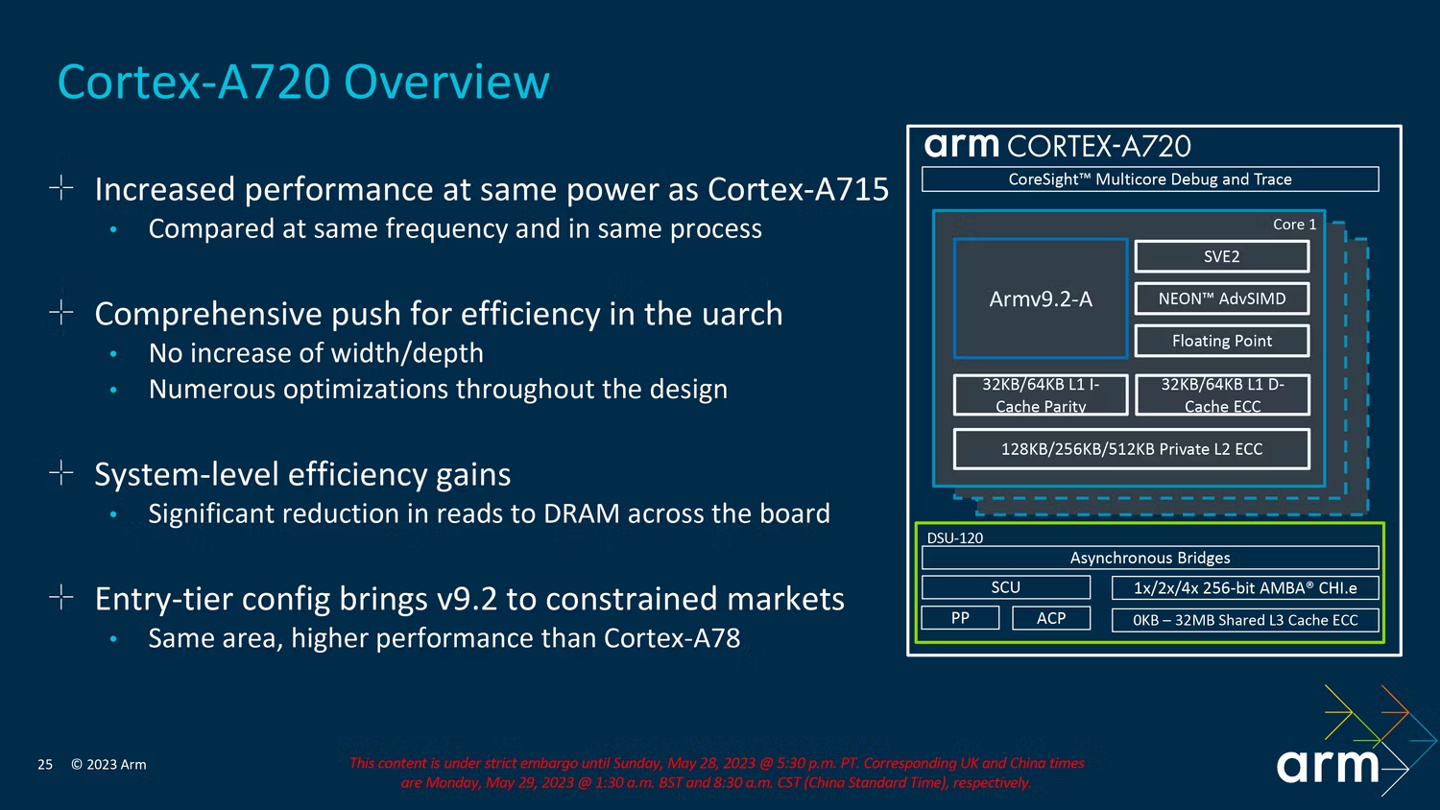

Cortex-A720 是 Arm 公司的性能核心,在與去年的 A715 相同的功率下,核心的效率提高了 20%,性能也有所提高。A720 核心主要平衡性能和功耗,一般會有四到六個這樣的核心用在芯片中。A720 核心在前端也做了一些改進,例如縮短了流水線長度,優化了分支預測,以及流水化了浮點除法和平方根運算。

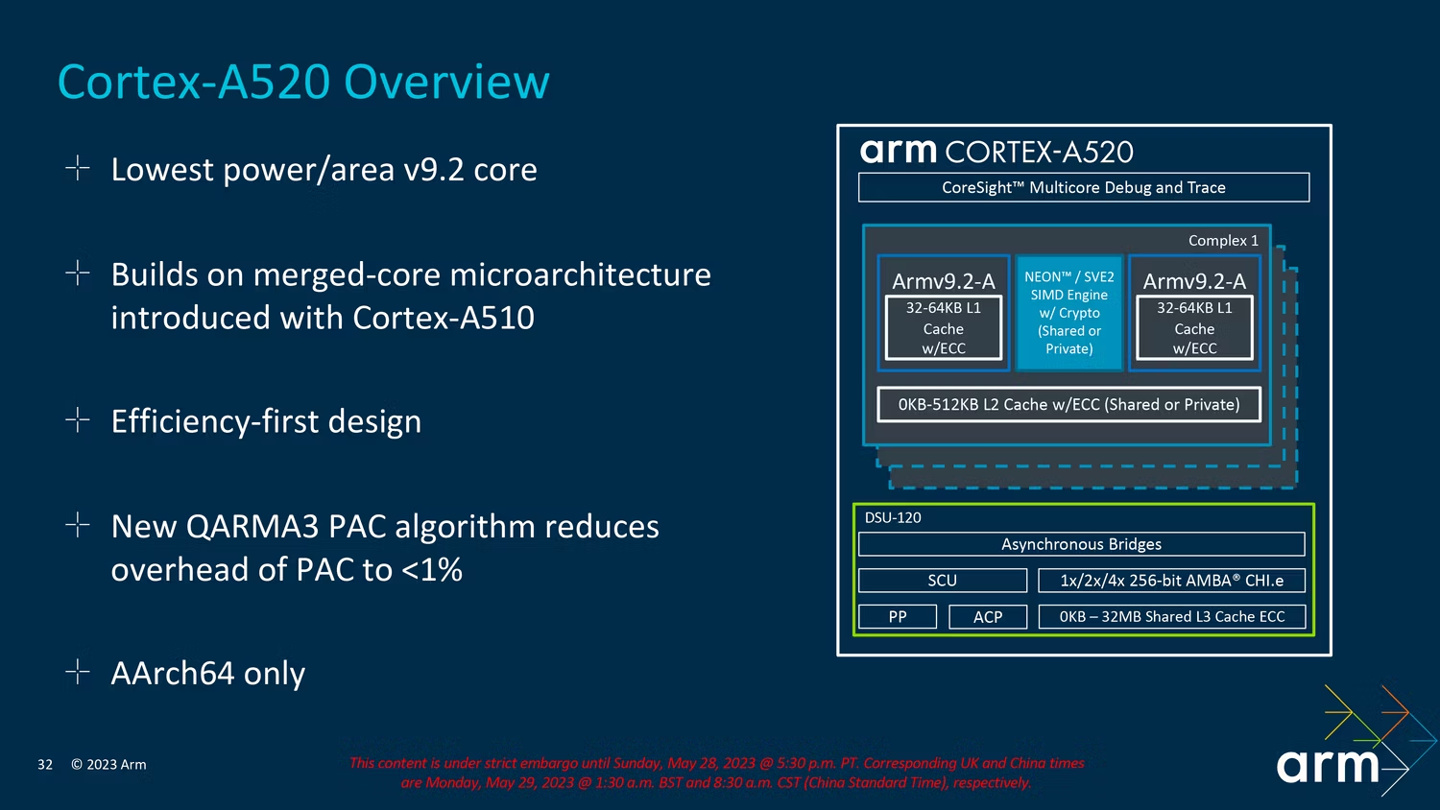

Cortex-A520 是 Arm 公司的效率核心,比去年的 A510 核心在相同性能下提高了 22% 的效率。A520 核心主要節省功耗和麪積,一般會有兩到四個這樣的核心在芯片中。A520 核心採用了合併核架構,可以在一個複合體中共享 L2 緩存、L2 轉換後備緩衝區和向量數據通路。A520 核心在前端也優化了分支預測,並移除或縮減了一些性能特性。

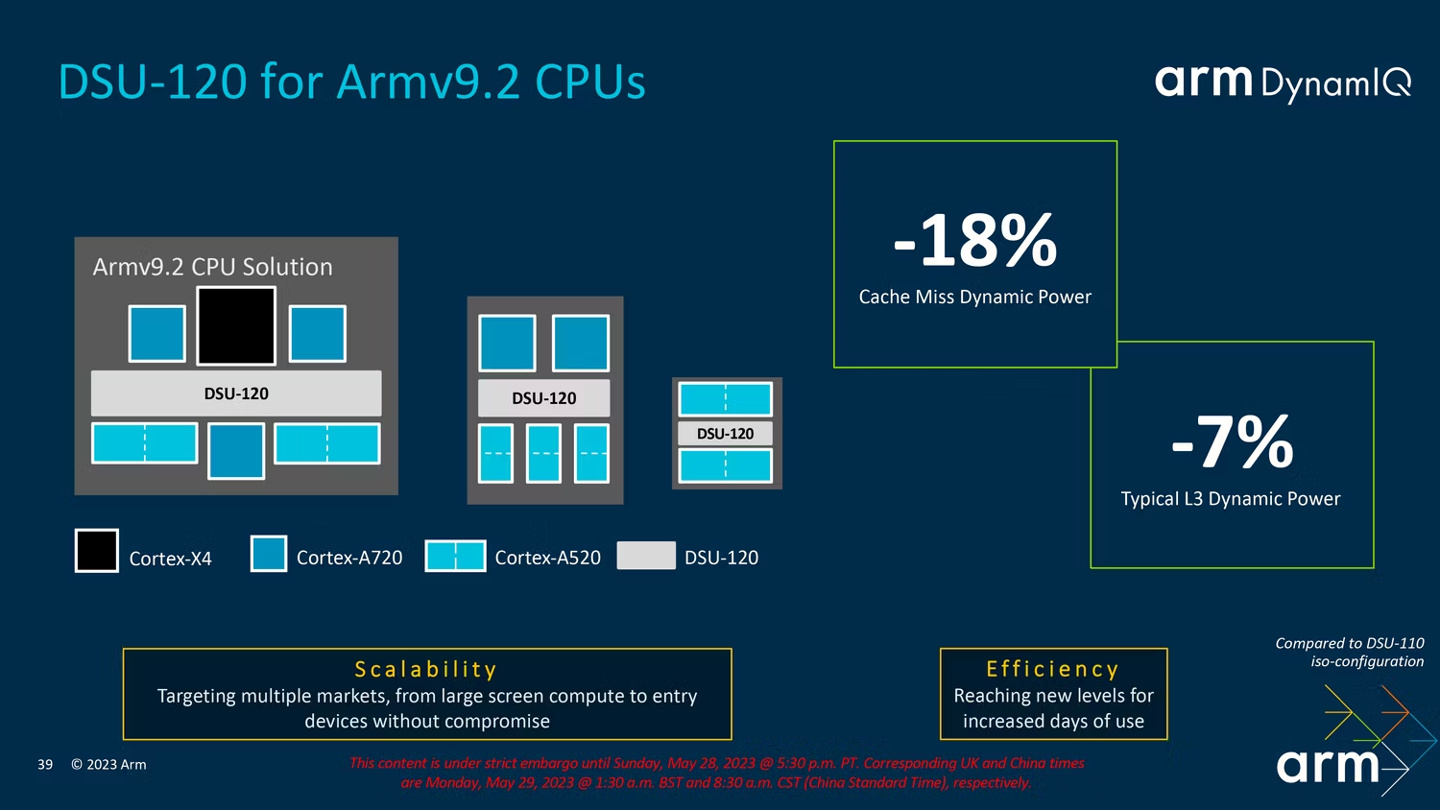

IT之家注意到,除了 CPU 核心之外,Arm 公司還更新了動態共享單元(DSU-120),這是一個將多個 CPU 核心與 L3 內存系統、控制邏輯和外部接口集成在一起形成一個多核集羣的模塊。DSU-120 相比 DSU-110 有多項改進,例如支持最多 14 個 CPU 核心(原來是 12 個),支持最多 32MB 的 L3 緩存。

Arm 公司表示,這些新的 CPU 核心設計是爲了應對移動設備市場的需求變化,不僅要追求更高的性能,還要考慮更好的效率、安全性和可擴展性。隨着Android系統對 64 位應用的要求越來越嚴格,Arm 公司認爲 64 位過渡已經“完成任務”,不再需要支持 32 位應用。

這些新的 CPU 核心設計預計將在今年底或明年初出現在新款芯片中,聯發科已經表示將在其下一代產品中使用該技術。

本文來源於:IT之家

更多遊戲資訊請關註:電玩幫遊戲資訊專區

電玩幫圖文攻略 www.vgover.com

![[極限競速:地平線 6] 豐田 Sport 800 '66 芬達聯動款領取攻略](https://imgheybox1.max-c.com/web/bbs/2026/04/02/f6bfcd46abba99d1714270672fb070ad.png?imageMogr2/auto-orient/ignore-error/1/format/jpg/thumbnail/398x679%3E)