在電子產品設計的世界裏,工程師們常常會提及一個關鍵而又略顯抽象的概念——“PCB阻抗控制”。對於許多初學者或外行人士來說,這似乎是一個深奧的技術細節。我們通常理解導線越通暢越好,爲何還要刻意去控制一種“阻力”呢?實際上,對於高速運轉的現代電子設備而言,阻抗控制並非可有可無,而是確保信號質量、產品性能乃至穩定性的生命線。

什麼是阻抗?它不只是電阻

要理解爲何要控制阻抗,首先要明白它是什麼。在直流電(DC)的世界裏,阻礙電流的是電阻(Resistance, R)。

但在交流電(AC)或高頻信號(本質上就是一種快速變化的交流電)的世界裏,情況變得更爲複雜。此時,阻礙電流的不僅有電阻,還包括由導線本身產生的感抗(Inductive Reactance, L)和由導線與周圍環境形成的容抗(Capacitive Reactance, C)。阻抗(Impedance, Z),就是這三者效應的綜合體現,可以理解爲信號在傳輸路徑上遇到的“動態綜合阻力”。

在PCB上,一根銅走線(Trace)並不僅僅是一條簡單的導線,它更像一個複雜的電子元件。它的阻抗值並非固定不變,而是由一系列物理參數共同決定的,包括:

•走線的寬度和厚度

• PCB板材的介電常數(Dielectric Constant)

•走線與下方參考平面(通常是接地層)之間的距離

•周圍其他銅皮或走線的形狀與距離

爲什麼要嚴格控制阻抗?信號傳輸的“高速公路法則”

如果將PCB上的信號傳輸比作在高速公路上行駛的汽車車隊,那麼阻抗控制就相當於爲這條公路設定了統一的“車道寬度”和“路面標準”。如果標準不一,會發生什麼?

1. 保證信號完整性,防止“交通事故”

當一個高速信號(如USB 3.0、PCIe或HDMI的數據流)在PCB走線中飛速傳播時,它期望整個路徑的阻抗是連續且恆定的。如果在中途,阻抗值突然發生變化(例如走線寬度突然改變),就會發生阻抗不匹配。

這種不匹配會像光從空氣射入水中發生折射和反射一樣,導致一部分信號能量被反射回源頭。這會造成災難性的後果:

波形畸變:反射回來的信號會與後續的原始信號疊加,導致接收端的波形出現過沖(Overshoot)、下衝(Undershoot)、振鈴(Ringing)等現象,也就是我們常說的毛刺和抖動。

數據錯誤:當波形畸變嚴重到一定程度,接收端的芯片將無法準確判斷信號是代表“0”還是“1”,從而導致數據傳輸錯誤,直接表現爲設備無法識別、藍屏、文件損壞或網絡掉包。

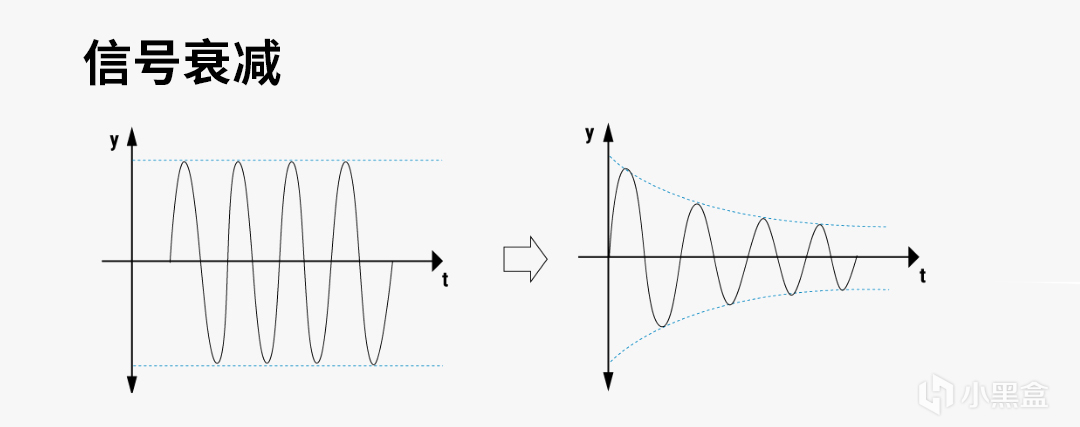

2. 減少信號損耗,確保“動力充足”

能量的傳輸效率在阻抗匹配時達到最大。想象一下,水流從一根粗水管進入一根細水管,在接口處必然會產生渦流和壓力損失,導致水流能量下降。同理,當信號在不同阻抗的路徑間傳遞時,就會發生能量損失,導致信號幅度衰減。在長距離傳輸或射頻信號應用中,這種損耗尤爲致命,可能導致信號到達終點時已微弱到無法識別。

3. 提升電路兼容性,實現“標準對接”

幾乎所有的芯片製造商在設計高速接口時,都會在其數據手冊(Datasheet)中明確規定其引腳的阻抗要求。這是一個行業標準,旨在確保不同廠商生產的設備能夠互相兼容。例如:

•USB、HDMI、PCIe等高速差分信號,通常要求PCB走線提供90Ω或100Ω的差分阻抗。

•射頻天線、視頻同軸電纜等單端信號,則普遍採用50Ω的單端阻抗標準。

•DDR內存總線的每一根地址和數據線,也需要嚴格的阻抗控制,以保證在極高頻率下所有數據都能同步、準確地被內存顆粒讀寫。

如果PCB設計沒有遵循這些標準,就會導致芯片與電路板之間“溝通不暢”,輕則性能下降,重則接口完全無法工作。

4. 避免電磁干擾(EMI),通過認證

阻抗不匹配點就像一個微型的天線。信號能量在此處發生反射和混亂,很容易以電磁波的形式向外輻射,形成電磁干擾(EMI),不僅會干擾設備內部的其他敏感電路,還可能干擾周邊的其他電子設備。這對於產品能否通過嚴格的EMC(電磁兼容性)認證至關重要。

綜上所述,PCB的阻抗控制遠非一個無關緊要的設計細節。它如同高速公路的“車道寬度”和“限速標準”,是爲高速信號流構建的一條平穩、順暢、無障礙的通道。通過精確控制走線的物理參數來實現特定的阻抗值,工程師們得以最大程度地避免信號反射、減少能量損耗、確保設備兼容並抑制電磁干擾。

因此,在高速數字和射頻設計領域,阻抗控制是決定產品成敗的關鍵因素之一,它直接關係到最終產品的穩定性、可靠性與性能表現。

更多遊戲資訊請關註:電玩幫遊戲資訊專區

電玩幫圖文攻略 www.vgover.com

![任天堂前銷售負責人預判:Switch 2 硬件漲價已成定局[cube_摘墨鏡][cube_摘墨鏡]](https://imgheybox1.max-c.com/bbs/2026/04/05/3b368916849076608f90f840878267fb.jpeg?imageMogr2/auto-orient/ignore-error/1/format/jpg/thumbnail/398x679%3E)

![[4.6]不亞於大促!50款1折佳作,3A大作,史低神作,你一定要看!](https://imgheybox1.max-c.com/web/bbs/2026/04/05/afe853848b2a0e8bee83b5effe9bf411.png?imageMogr2/auto-orient/ignore-error/1/format/jpg/thumbnail/398x679%3E)