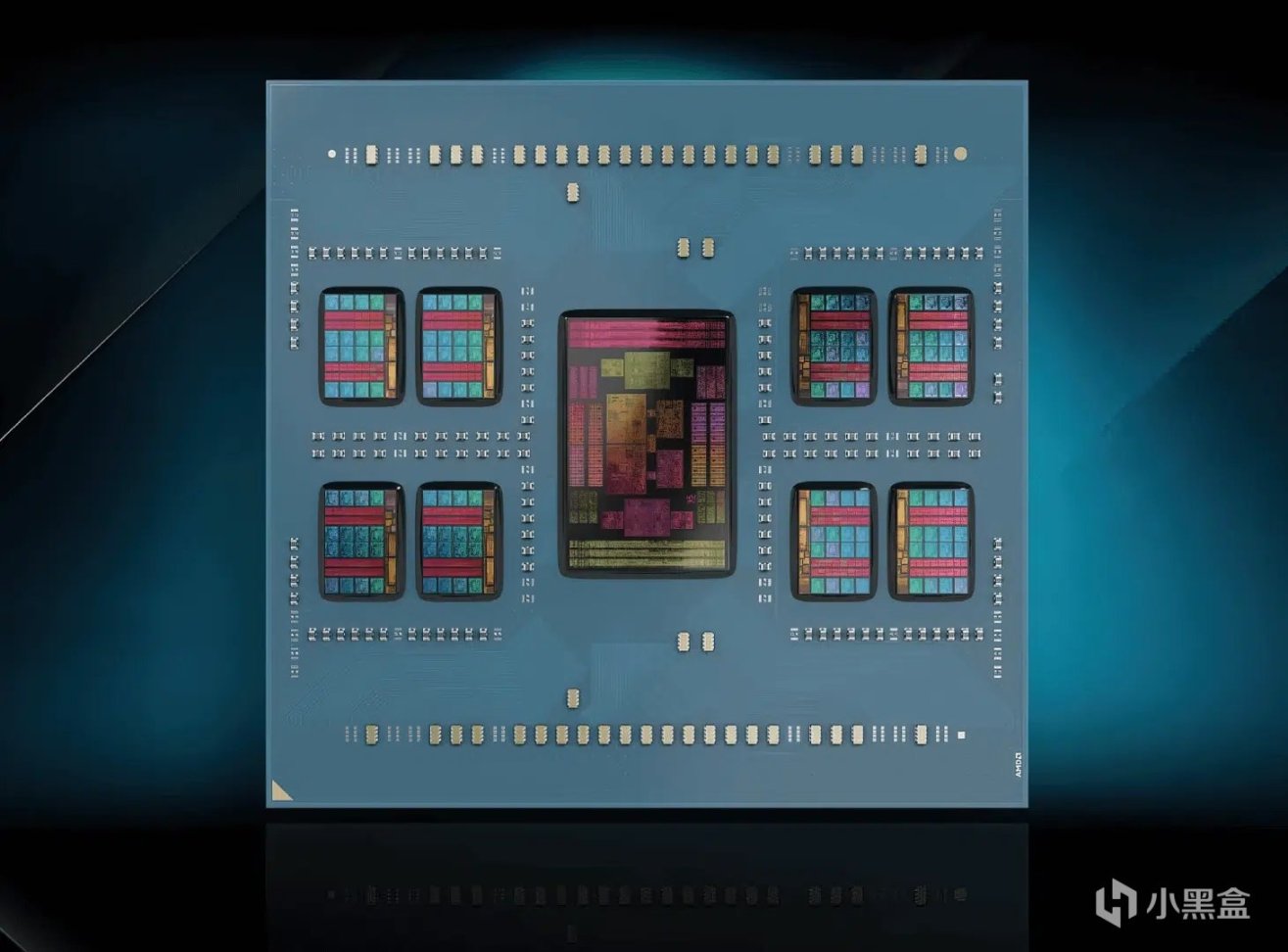

AMD即將發佈首款混合核心處理器,在Arm中也稱爲big.LITTLE,這些APU代號爲Phoenix2,包含銳龍7040系列,具有更小的芯片面積和更高的能效,在下圖中,左側爲vanillaPhoenix,右側爲Phoenix2由於Zen4c核心較小,後者比前者緊湊23%

AMD異構核心架構方法比英特爾的方法簡單得多,AMD沒有使用完全不同的ISA(如英特爾的Monts),而是決定使用縮小的Zen4核心,這帶來了同樣的優勢,減少芯片空間提高電源效率,而無需維護第二個ISA

據BusAlexeyPhoenix2稱,這些高端芯片是雙源的,由一些完全啓用的Phoneix2芯片組成,而其餘的則由精簡的Phoneix芯片衍生而來,Phoenix2芯片上的Zen4c核心是以較低頻率運行的精簡版Zen4核心,目前尚不清楚3級緩存是否已進一步減少,或者佈局規劃是否針對芯片空間進行了優化

這種安排允許AMD降低Pheonix芯片上的核心的頻率,Phoenix 2系列中,銳龍7540U是旗艦Phoenix2芯片,配備兩個支持高核心頻率的Zen4核心和四個以較低頻率運行的Zen4c核心,以提高能效

與其他芯片上的Zen4c核心不同,霄龍貝加莫的每個CCD均由16核組成,是普通Zen4 CCD的兩倍,而Phoenix2 CCD只是經過改造的8核CCD,混合使用8核和16核CCD的移動銳龍的類似設計,不確定具體參數

除了6核16線程之外,基於Phoenix2的銳龍7540U還由4個RDNA3計算單元組成,只有高端Phoenix芯片(最多12個CU)的一小部分,但考慮到芯片面積的減少,這也比較合理

AMD銳龍Phoenix2移動處理器於假期時上市,數量有限,用於專門用於手持設備和定製OEM筆記本電腦

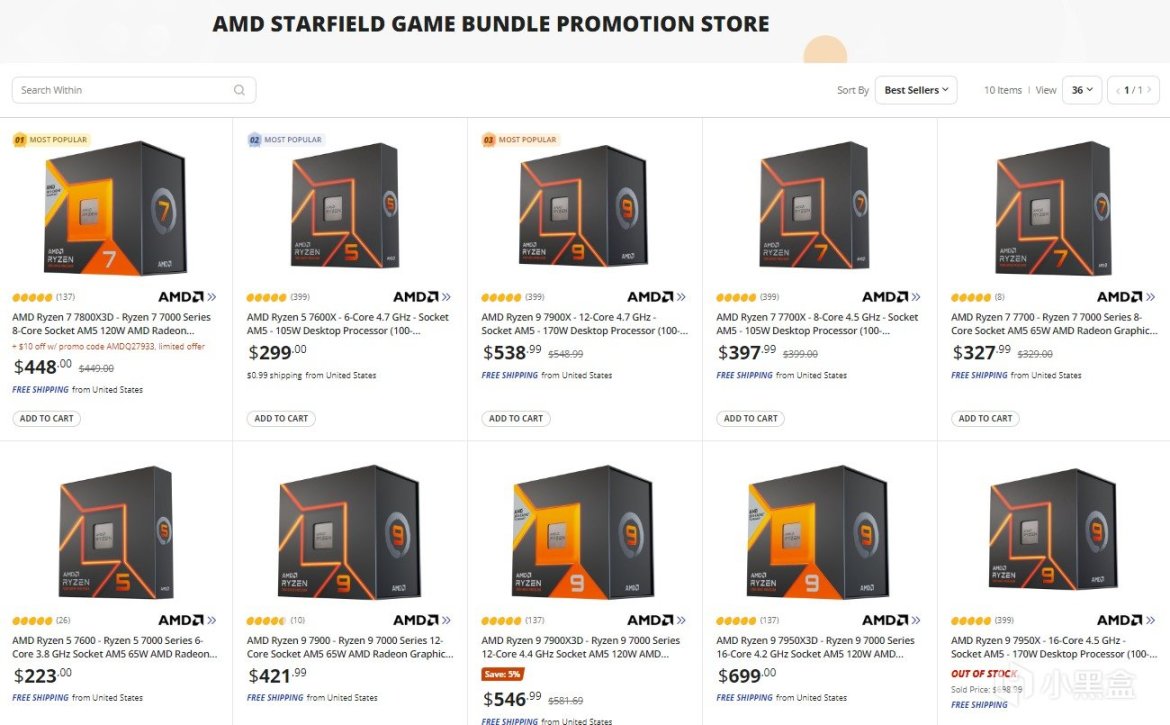

此外,AMD把星空與銳龍7000系CPU系列捆綁銷售

一位勤奮的讀者最近發現,Neweggs上出現了一個新的遊戲捆綁頁面,這一進展強烈表明,AMD即將推出新的遊戲捆綁包,包括遊戲《星空》,讓這一消息變得更加耐人尋味的是,AMD上週與遊戲開發商Bethesda建立關係

促銷頁面顯示,銳龍7000系的所有CPU都有資格參加這次即將推出的促銷活動,提到的具體CPU如下:

顯卡遊戲捆綁包是之前的促銷活動(包括最後生還者第一部分)已於5月底結束,以星球大戰絕地倖存者爲特色的銳龍7000系捆綁包已於6月30日終止,星空遊戲捆綁包很快就會公佈,可能是下週初

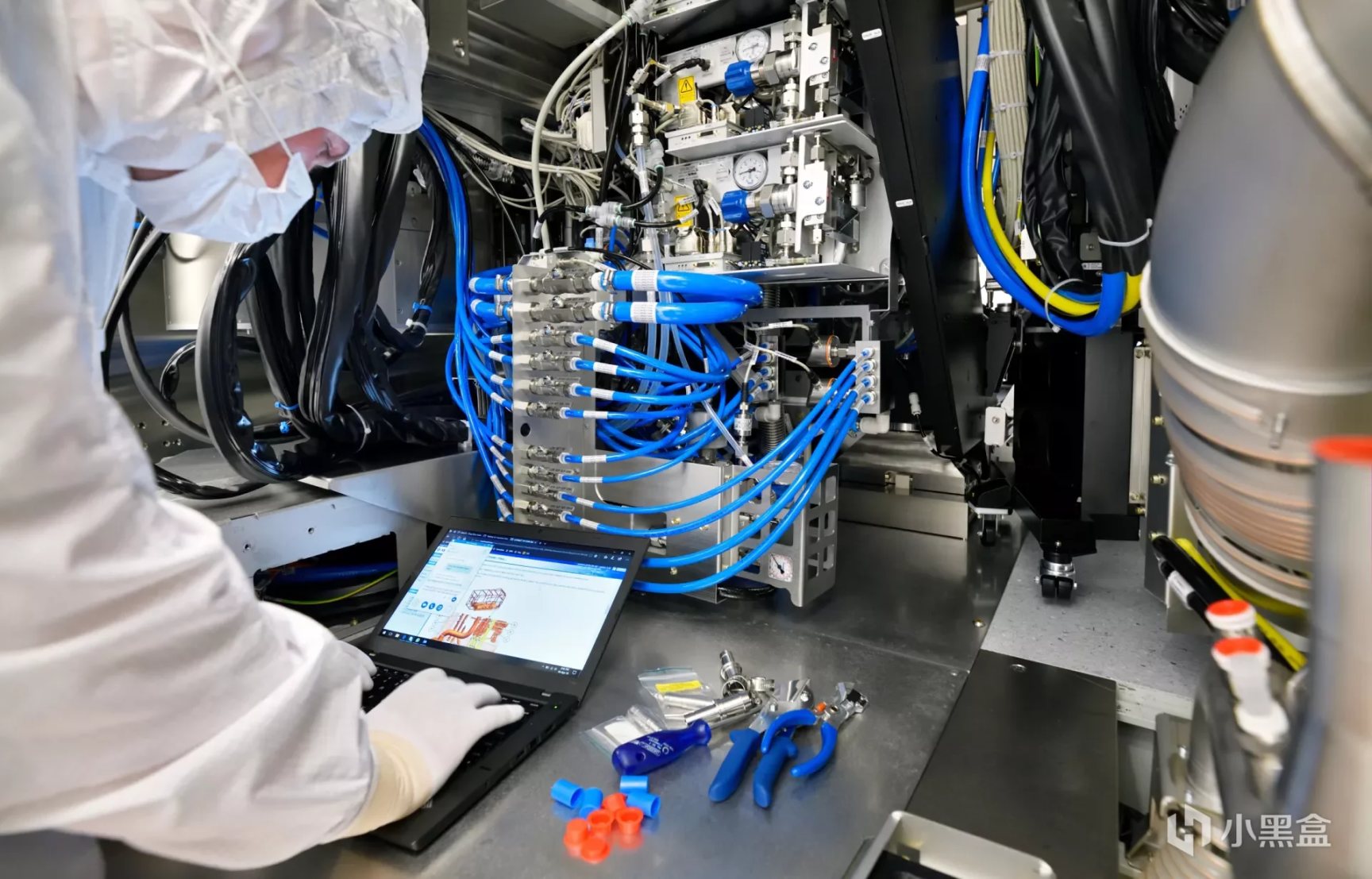

此外,荷蘭新出口規則濫用出口管制

荷蘭週五對用於製造芯片的先進工具實施額外出口管制後,中國駐荷蘭大使館發表公開信,強烈反對這一決定,要求扭轉這一決定。呼籲荷方從維護國際貿易規則和雙邊經貿的大局出發,立即糾正錯誤做法

應要求,荷蘭本週大幅擴大了受制裁工具清單,DUV機器納入中,從而限制了中國的准入。過去,只有EUV機器的訪問受到限制,因此限制更常見的DUV機器的舉措是受制裁機器清單的擴大

中國大使館批評此舉濫用出口管制措施,破壞自由貿易和國際貿易規則,大使館進一步強調了對國內和荷蘭企業的潛在損害,警告供應鏈會受到干擾

還指責某個大國—操縱盟友對國內進行經濟遏制,使館敦促荷方立即糾正行爲,方堅定維護自身權益,與荷方,促進中荷經貿關係的互利共贏

荷蘭制定計劃於9月1日生效的新出口規則要求,光刻掃描儀制造商ASML必須獲得出口許可證,才能向國內銷售Twinscan NXT:2000i和更先進的掃描儀。該掃描儀採用深紫外(DUV)光刻技術,可生產採用7納米和5納米級工藝技術的芯片

荷蘭以國家安全爲名對國內半導體的限制不像去年10月美實施的那麼嚴格,這些出口法規要求可以使用USA工具和許可證,這些工具和技術可用於生產14nm/16nm及以下節點的非平面晶體管邏輯芯片、128層或以上的3DNAND以及18nm半的內存顯存芯片。規則要求美公民必須獲得爲國內半導體工作的許可證

光刻工具是芯片工廠中使用的最複雜的設備之一,ASML是這個方面的專家無可爭議,國內企業需要幾十年的時間才能趕上Twinscan NXT:2000i。與此同時,沒有應用材料、KLA和LamResearch等的工具,無論如何都不造不出現代技術的生產芯片

荷蘭的新規定不會對國內半導體產生重大影響,特別是考慮到中芯國際是唯一一家能夠採用14納米級工藝技術和更薄技術製造芯片商,但這一消息卻引發了國內駐荷蘭大使館的強烈反對

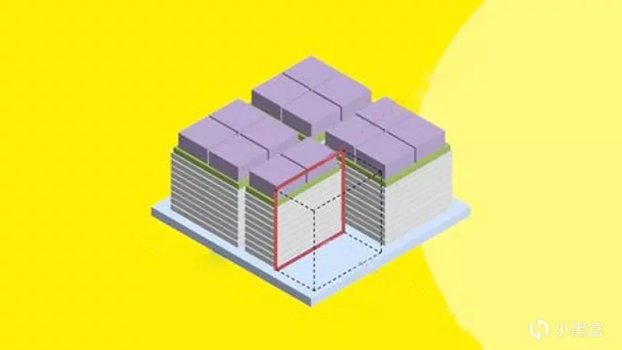

此外,內存顯存方面,研究人員稱混合3D內存可以提高CPU和顯卡之間的帶寬

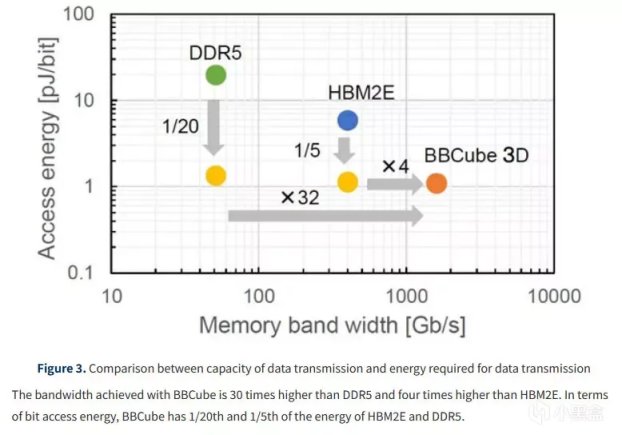

東京工業大學的研究人員概述了他們的新型BBCube混合3D存儲器,BBCube3D是Bumpless Build Cube3D的縮寫,這種新型內存可以通過提高處理單元性能(或PU,顯卡和CPU)與顯存芯片之間的帶寬,爲更快、更高效的計算鋪平道路,該技術提供DDR5的4倍帶寬和HBM2E的30倍帶寬。重要的是,它還通過位訪問能量減少到DDR5內存的二十分之一,以及HBM2E所使用的能量的五分之一,提供非常不錯的能耗比

東京工業大學官方新聞博客宣稱,BBCube3D的堆疊架構已經實現了全世界可達到的最高性能,在解釋BBCube3內存的設計方式之前,研究人員說明了使用DDR5或HBM2E等當前可用內存技術所面臨的問題。他們斷言,目前理想的更高帶寬是以昂貴的更寬總線一個或兩個爲代價的,或者是功耗密集型數據速率提升的代價

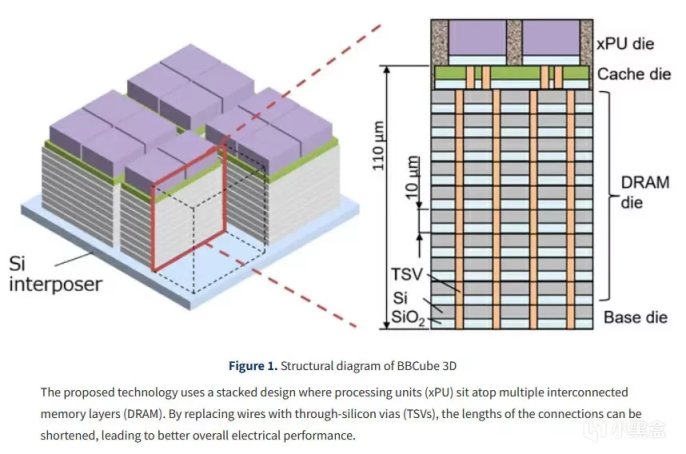

那麼,BBCube3D如何提高PU和動態隨機存取存儲器(內存)之間的集成度呢?下圖給出了BBCube3D設計的基本概述。Pus位於內存堆棧旗艦緩存之上,這些都在硅中介層基礎上

缺乏典型的焊料微凸塊,以及使用TSV代替較長的電線,共同有助於實現低寄生電容和低電阻,該結構在PU和內存之間建立了三維連接,廣泛使用了硅通孔(TSV)

東京工業大學稱BBCube3D的性能使其對計算設計極具吸引力,這要歸功於性能和減少能源消耗的令人信服的結合。該設計的理想質量源於電源效率,可以減少熱管理和電源問題,解決某些3D半導體設計會引發的這種問題

目前還沒有BBCube3D商業化的計劃,因此東京工業大學的科學家起希望這項新技術可以更快、更高效的爲計算鋪平道路

更多遊戲資訊請關註:電玩幫遊戲資訊專區

電玩幫圖文攻略 www.vgover.com

![任天堂前銷售負責人預判:Switch 2 硬件漲價已成定局[cube_摘墨鏡][cube_摘墨鏡]](https://imgheybox1.max-c.com/bbs/2026/04/05/3b368916849076608f90f840878267fb.jpeg?imageMogr2/auto-orient/ignore-error/1/format/jpg/thumbnail/398x679%3E)

![[4.6]不亞於大促!50款1折佳作,3A大作,史低神作,你一定要看!](https://imgheybox1.max-c.com/web/bbs/2026/04/05/afe853848b2a0e8bee83b5effe9bf411.png?imageMogr2/auto-orient/ignore-error/1/format/jpg/thumbnail/398x679%3E)