来源——AMP实验室

蓝色方还有活路吗?

不久之前,AMD发表新的突破性声明,宣布与台积电建立长期合作关系,并且确认采用最新的制造技术和工艺节点生产其下一代霄龙CPU:

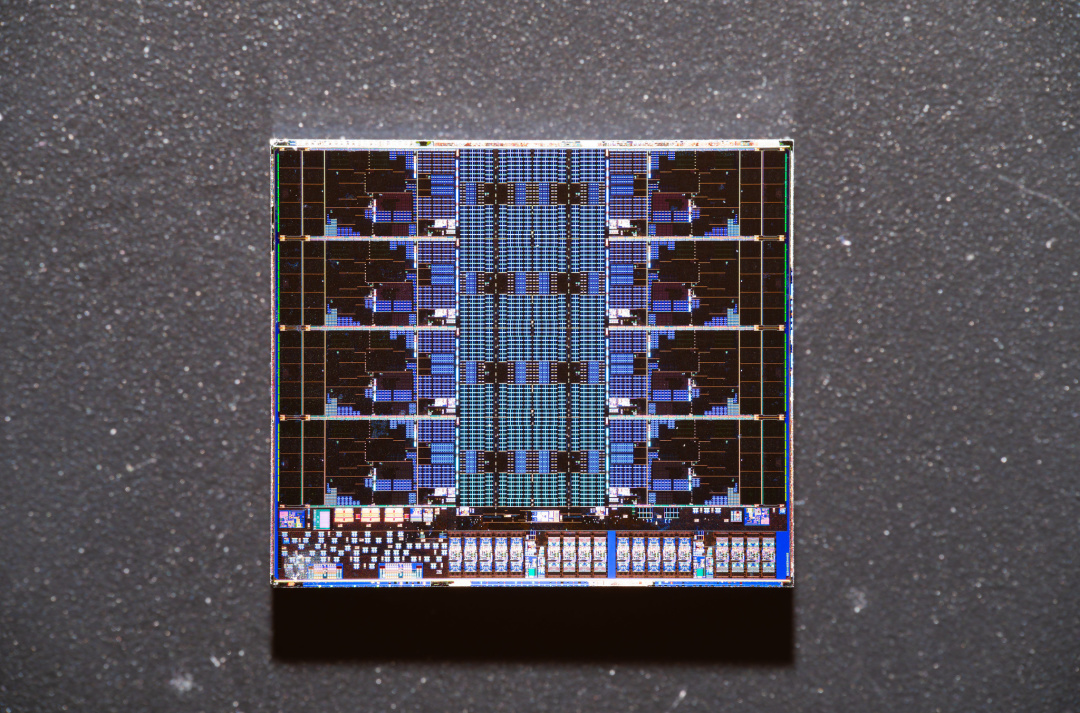

第六代霄龙EPYC代号“Venice”,也就是水城威尼斯,这将成为业界首款采用台积电N2工艺进行流片和升级的HPC(超级计算机)产品。台积电将在其N2制程上采用NanoSheet技术,为ZEN6和ZEN6C等新设计架构进行协同优化,计划于明年推出。

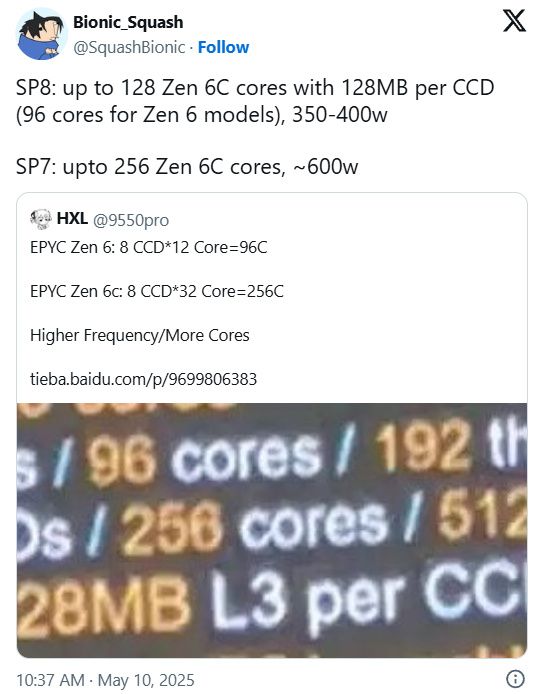

最新爆料来自twi@9550pro 和twi@squashbionic,这次消息这证实Venice将采用最多8个CCD的配置方式,而CCD芯片分为了ZEN6和ZEN6C两种核心设计。

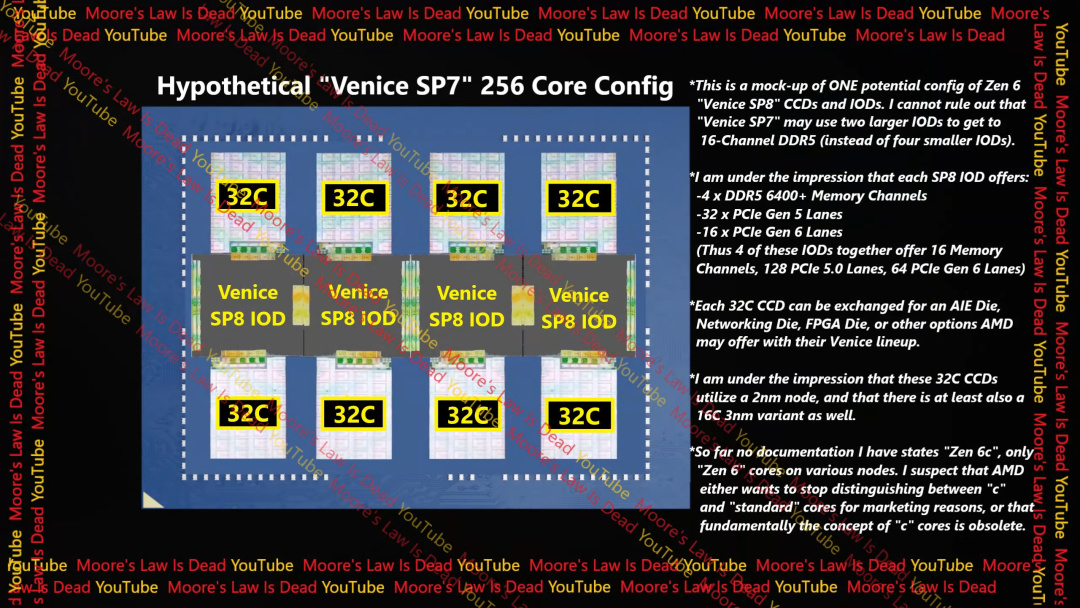

重要的是,第一种常规CCD,也就是会通用在正统消费级锐龙和数据中心霄龙上的CCD,将升级到单个芯片内12核心;第二种高密度CCD,也就是ZEN6C,用于数据中心高密度计算和某些锐龙APU上的芯片,将提升至单颗集成32核心——这意味着在新EPYC霄龙“Venice”上,配置将拥有两种超级旗舰,包含96个ZEN6核心和256个ZEN6C核心,提供192线程和512线程。

此外,消息还证实,ZEN6 CCD因为规模提升,L3缓存从原本的32MB提升至48MB,而ZEN6C CCD则大增L3缓存到128MB,也就是说,高密度ZEN6C霄龙旗舰将实现无X3D技术加成下的1GB L3缓存!

不过比较遗憾的是,新ZEN6霄龙并不能无缝过渡,而是需要新的SP7和SP8平台,这一消息在2023年便有所流传。其中SP7平台支持最多16通道内存,可支持ZEN6的96核心霄龙旗舰或ZEN6C的256核心高密度霄龙旗舰,其TDP设计提升到600W;SP8平台则限制为了ZEN6的96核心霄龙旗舰或ZEN6C的128核心高密度霄龙,支持8通道内存,定位于入门级服务器解决方案。

众所周知,消费级锐龙处理器本质也是来自霄龙的边角料,它们共用同一套CCD芯片。所以新消息对消费级的意义在于,在下一代ZEN6架构正统续作锐龙上,可以看到消费级R5的8核16线程、R7的12核心24线程以及旗舰的24核心48线程,或许还能等来R3锐龙回归,提升成为6核12线程。

除了核心提升,还有一点就是L3缓存的扩充,新增加的缓存容量,让玩家们即使不购买X3D处理器,也能拥有可观的高速缓存,这可以让新消费级普通锐龙更加贴近X3D锐龙的帧数表现。

而接下来AMD的Event,除了在本月20日~23日台北举办的Computex2025上发表主题演讲 ,还有即将在6月12日的Advancing AI大会,届时可以看到AMD对下一代架构的讨论以及最新霄龙EPYC“Venice”的预告。

更多游戏资讯请关注:电玩帮游戏资讯专区

电玩帮图文攻略 www.vgover.com